Descriere produs

Diferența între cvasi-industriale și industriale la nivel de:

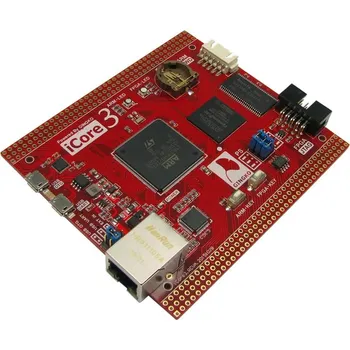

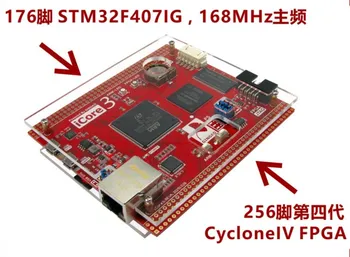

Cea mai nouă versiune de iCore (ICore3 Trei generații) caracteristici după cum urmează:

1, clasic ARM+FPGA structura este încă folosit, iar cele două sunt conectate printr-FSMC de autobuz.

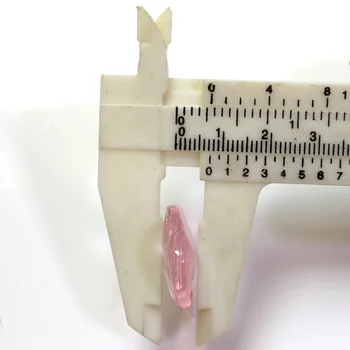

2, rosu Shen aur patru laminat, dimensiunea 10.16 X 9 cm;

3, BRAȚUL actualizat la 176 pin M4 cip (STM32F407IGT6) a unei performanțe mai mari și mai multe ace.

4. FPGA adoptă patra generație Ciclon EP4CE10F17C8N și 256 pini BGA.

5, BRAȚUL de expansiune externă pin ajunge la 68 individuale; standard 2.54 acul cu gămălie este selectat pentru a facilita experiment.

6, FPGA expansiune externă pin ajunge 105individual; standard 2.54 acul cu gămălie este selectat pentru a facilita experiment.

7. Built-in de mare viteză interfață USB OTG, ca Dispozitiv de comunicare de viteză se apropie de 40 de milioane de bytes / sec; și poate citi discul U (prin banda de transfer de cabluri);

8. Construit în 100MEthernet circuit.

9. Construit în USB interfață UART, poate fi folosit pentru depanare de fundal.

10, alimentare pot fi furnizate de către ac (5V putere), și pot fi furnizate direct de către interfață USB.

11. FPGA sprijină PS modul de configurare.FPGA poate fi configurat de braț, iar rutina de Ethernet bazate pe, U-disk-bazat și TF-card bazate pe FPGA de configurare pot fi furnizate.

12. Built-in dual-active oscilator de cristal, USB strat fizic, USB to UArt, Ethernet chip, BRAȚ, FPGA și alte mari chips-uri sunt folosind active oscilator de cristal pentru a asigura funcționarea fiabilă;

13, construit în două butoane individuale, care sunt conectate la BRAȚ și FPGA respectiv.

14, construit în două Trei LED-uri de culoare de instrucțiuni, respectiv pe BRAȚ și FPGA;

15, TF card holder cu built-in SDIO interfață; furnizarea de rutină, bazate pe FATFS sistemul de fișiere;

ICore3 de bază experiment de rutină indicele de masă de Serie BRAȚUL de rutină [toate] FPGA de rutină [toate] 1 RoutineOne:BRAȚUL driver LED în Trei culori RoutineOne: știu FPGA 2 RoutineTwo: citește brațul butonul de stare RoutineTwo:GPIO ieșire experiment-aprinde LED în Trei culori 3 RoutineThree:EXTI întrerupe intrare experiment ... citește BRAȚ buton de stat RoutineThree:GPIO intrare experiment de recunoaștere taste de intrare 4 Rutină patru: USART comunicare experiment-comanda LED control de Rutină patru: Tcl script experiment-configurare pin 5 de Rutină cinci: SYSTICK timer experiment-iluminat cu LED-uri la intervale regulate de Rutină cinci: Semnal Tapll experiment-analizor logic 6 Rutină șase: IWDG watchdog experiment-resetare BRAȚUL de Rutină șase: counter experiment-contor de utilizare 7 Rutină șapte: WWDG watchdog experiment-resetare BRAȚUL de Rutină șapte: de bază poartă logică experiment-utilizarea de porți logice 8 Rutină opt: timer PWM experiment-respirație lampa de Rutină opt: trigger experiment-utilizarea de declanșare 9 Rutină nouă:ADC experiment-alimentare de monitorizare de Rutină nouă: mașină de stat experiment-utilizarea de mașină de stat 10 Rutină zece: ceas de timp real RTC experiment - afișare data și ora de Rutină zece: phase-locked loop experiment-phase-locked loop 11 Rutină zece Una:DMA experiment-transmiterea de memorie de memorie de Rutină zece Una: multiplicator experiment-multiplicator de utilizare 12 Rutină zece Doi: universal timer experiment-temporizat iluminare LED de Rutină zece Doi:Modelsim experimentului de simulare 13 Rutină zece Trei:SDIO experiment-citire SD card-informații de Rutină zece Trei:FSMC comunicare bus -- experiment multiplex adresa modul 14 Rutină paisprezece: FATFS experiment-operațiune de fișier de Rutină paisprezece: FSMC comunicare bus -- experiment independent adresa mode 15 de Rutină Cincisprezece: USB_CDC experiment-de mare viteză de transmisie a datelor de Rutină Cincisprezece: comunicare experiment între BRAȚ și FPGA bazat pe USART 16 Rutină Șaisprezece: USB_HID experiment-două-mod de transmitere a datelor de Rutină Șaisprezece:comunicare experiment între BRAȚ și FPGA bazat pe SPI autobuzul 17 Rutină șaptesprezece: USB_MSC experiment-citire / scriere pe disc U (memorie de mare capacitate) de Rutină șaptesprezece: comunicare experiment între BRAȚ și FPGA bazat pe magistrala I2C 18 Rutină Optsprezece: USB_VCP experiment-port serial virtual de Rutină Optsprezece: ARM+FPGA de acces la date experiment bazat pe un singur port RAM 19 Rutină Nouăsprezece: USBD_MSC experiment-Virtuale U disc de Rutină Nouăsprezece: ARM+FPGA de acces la date experiment bazat pe dual port RAM 20 RoutineTwo zece: LAN_TCPC experiment-transmisie de date Ethernet RoutineTwo zece: FIFO bazate pe ARM+FPGA de acces la date experiment 21 RoutineTwo zece Una:LAN_TCPS experiment-transmisie de date Ethernet RoutineTwo zece Una:Niosii -- construi Oneindividual moale core bazat pe RAM internă 22 RoutineTwo zece Doi:LAN_UDP experiment-transmisie de date Ethernet RoutineTwo zece Doi:Niosii -- program de întărire a SPE 23 RoutineTwo zece Trei:LAN_HTTP experiment-server web RoutineTwo zece Trei: foloseste JTAGUART terminal pentru a imprima informații. 24 RoutineTwo paisprezece: LAN_DHCP experiment-alocarea dinamică de adrese IP RoutineTwo paisprezece: Niosii -- SDRAM citire și scriere experiment 25 RoutineTwo Cincisprezece: LAN_DNS experiment-nume de domeniu rezoluție RoutineTwo Cincisprezece: NIOS II UART serial de comunicare experiment 26 RoutineTwo Șaisprezece: MODBUS TCP experiment-alimentare de monitorizare RoutineTwo Șaisprezece: SDRAM de scriere și citire a testa experiment 27 RoutineTwo șaptesprezece: DMA LAN experiment-de mare viteză de transmisie de date de măsurare a vitezei RoutineTwo șaptesprezece: Design TFT driver bazat pe SDRAM 28 RoutineTwo Optsprezece: FSMC experiment-Citirea și scrierea FPGA RoutineTwo Optsprezece: Design de VGA driver bazat pe SDRAM 29 RoutineTwo Nouăsprezece: SD_IAP_FPGA experiment-update și upgrade FPGA 30 RoutineThree zece: U_DISK_IAP_FPGA experiment-update și upgrade FPGA 31 RoutineThree zece Una:HTTP_IAP_FPGA experiment-update și upgrade FPGA 32 RoutineThree zece Doi:UART_IAP_ARM experiment-- update și upgrade STM32 33 RoutineThree zece Trei:SD_IAP_ARM experiment-update și upgrade STM32 34 RoutineThree paisprezece: U_DISK_IAP_ARM experiment-update și upgrade STM32 35 RoutineThree Cincisprezece: HTTP_IAP_ARM experiment-update și upgrade STM32 36 RoutineThree Șaisprezece: DAC experiment-ieșire tensiune DC 37 DEMO1.0 program de testare eliberarea 38 ICore3 aplicație: exemplu de aplicare encoder bazat pe ICore3 dual core placa